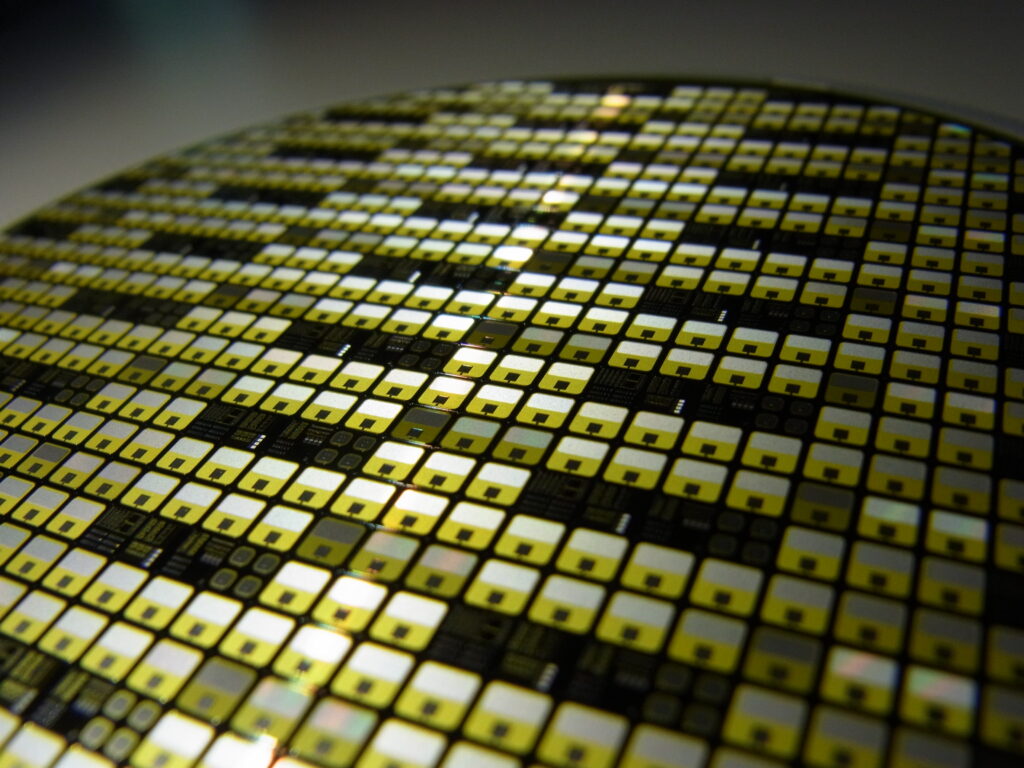

デバイス分科会ではSiCおよびGaNを基板材料とした次世代パワーデバイスの研究開発に取り組んでいます。デバイス試作ラインはSiCとGaNの4インチウエハが併用可能な世界で唯一の量産レベルの試作ラインです。ここで多くのプロセスレシピを創出し蓄積しており、それらを活用することで新しいデバイス開発において、研究着手から事業化判断までの大幅な期間短縮を可能にしています。SiCでは既に660V~20kV超の耐圧クラスで、SBD、Planer MOSFET、Trench MOSFET、SBD内蔵MOSFET、SJ-MOSFET、PiN Diode、IGBTのデバイス開発に成功し、企業への技術移転を経て実用化に至った例もあります。またラインのSiCとGaNの併用化によって、GaNのPN-diode、SiC DiodeとGaN HEMTのハイブリッドデバイスも4インチウエハでの試作実証に成功しています。これら新規デバイス開発を下支えする要素技術として、特にゲートMOS界面の開発・評価も重視しています。SiCとGaNのMOS界面を同じ環境で作製し共通のTEGで同一水準で比較することで、将来技術に対するポテンシャルの見極めが可能になると考えています。

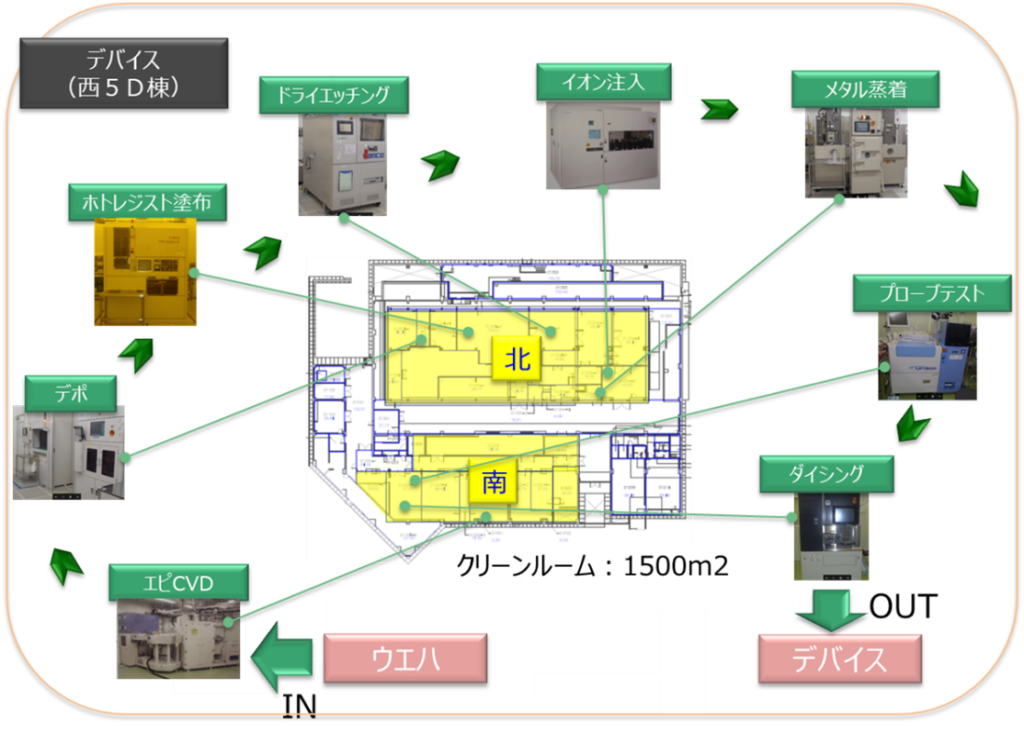

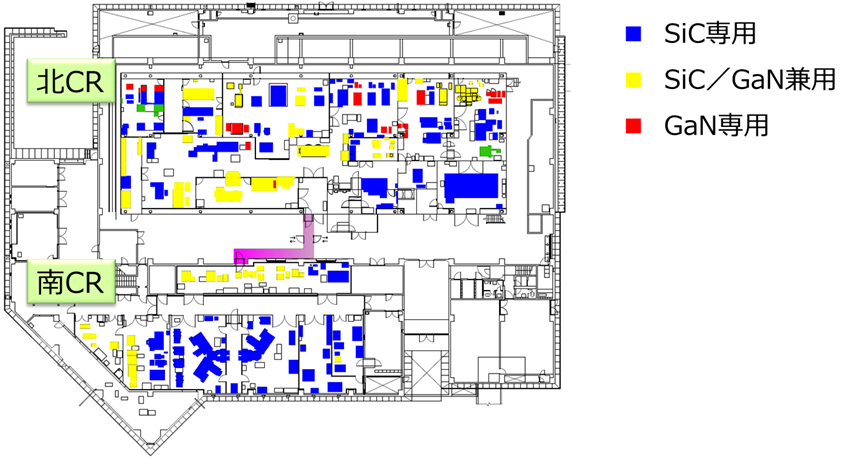

施設・設備

産総研西事業所5D棟に1500 m2の4インチデバイス試作ラインを完備し、SiCのエピタキシャル装置からプローブテスト、ダイシングまでの一貫プロセスラインを構築しています。また、装置群をSiC専用、SiC/GaN共用、GaN専用に分類し、共用装置のクリーニング方法を確立することで、SiCとGaNのコンタミを回避する運用をしています。2024年下期からは小片チップでのプロセスも可能となり、要素技術開発を効率化も図ります。

研究開発テーマ例

SiCパワーデバイス

SiCパワーデバイスの本格実用化に向け、低オン抵抗化、高信頼化を重点課題に取り組んでいます。これまで、プレーナーゲートとトレンチゲートMOSFETの開発および社会実装に成功し、ショットキー内蔵型MOSFETの独自構造であるSWITCH-MOSを開発してきました。近年では更なる低オン抵抗化を目指し、世界に先駆けてスーパージャンクションMOSFETの開発を行っています。

SiCパワーIC

SiCパワーデバイスの更なる損失低減には、高速スイッチングによるスイッチング損失の低減が必要です。パワーデバイスとそれを駆動するゲートドライバ近接配置することによる高速制御技術の究極的な形態として、SiCのCMOS駆動回路と縦型パワーデバイスを同一チップに集積したSiCモノリシックパワーICを開発しています。開発の難しいSiC pチャネルMOSFETについて、独自の特性改善技術を有しており、世界で初めてSiCモノリシックパワーICのスイッチング動作に成功しました。

GaN, GaN&SiCハイブリッド

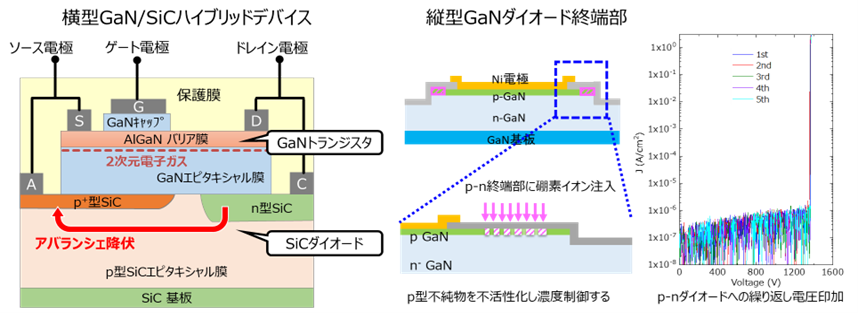

GaN半導体は高い伝導特性、高速なスイッチング特性を持ち、従来に比べてより低損失かつ小型なパワーエレクトロニクス機器が実現できると期待されています。しかし、パワーデバイスに必須のpn終端構造はプロセス上の課題で実現していません。これによって縦型、横型デバイス構造共に電圧印可に対して脆弱なことで、車載用など高い信頼性が要求される応用への展開が進んでいません。私たちはSiCデバイス開発で培った技術を活用するなど、強みを生かした独自のアプローチで課題を解決し、高信頼GaNパワーデバイスの実用化、および適用範囲拡大を目指しています。

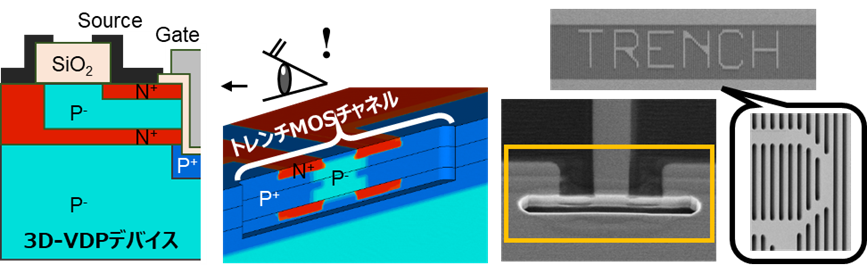

ゲートMOS界面研究

SiCトレンチMOSチャネルの特性は、複雑なパワーデバイスプロセスを経て実デバイスに組み込まれるため、コントロールされた要素実験と異なる可能性があり、測定も困難を極めるため正確に調べられていませんでした。そこで私たちは、SiCトレンチMOSチャネルの直接評価を可能にするオリジナルの「3D-VDP素子」を、TPECの高度なデバイスプロセス技術を活用して新規開発しました。基礎学理の観点に立脚しながら、実デバイスレベルで優れた特性を得るため手法を追求しています。